目前的電腦運算建構在傳統馮諾伊曼(von Neumann)架構,數據資料必須在運算單元與記憶體間進行反覆的傳輸,不僅限制運算效能,更造成大量的能量耗損。記憶體內運算(In-Memory Computing)乃至於次世代仿大腦運作的神經形態運算(neuromorphic computing)均是突破馮諾伊曼限制的運算架構,而這些創新的運算架構極為仰賴新型態記憶體的開發。由於鐵電記憶體(Ferroelectric Memory, FeFET)實現多位階(multi-level cell)、突觸權重(synaptic weight)調整對稱性、精準性、元件均勻性、操作速度、功率消耗與積體電路製程相容性相較於其他新形態記憶體極具有競爭優勢,因此近年來受到學界與業界高度的矚目。

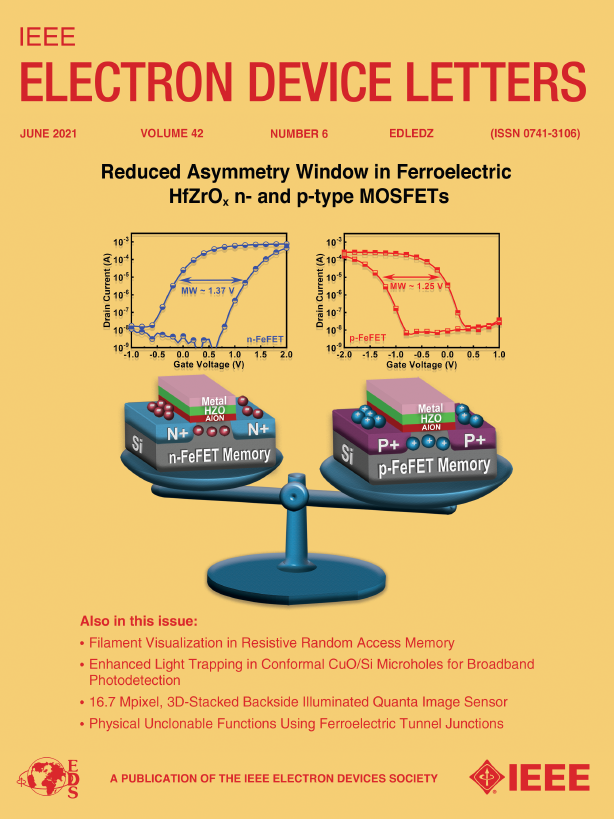

儘管鐵電記憶體的效能已有相當程度的提升,但n型與p型鐵電記憶體極不對稱的記憶視窗(memory window)卻大幅限制了鐵電記憶體在記憶體內運算或神經形態運算的應用。有鑒於此,清華大學工程與系統科學系巫勇賢教授團隊與國家同步輻射研究中心吳品鈞研究員團隊提出在矽晶圓上以前瞻的氮氧化鋁(AlON)介面層整合5 nm超薄的HfZrOx鐵電層應用至n型與p型鐵電記憶體,不僅有效地克服了記憶體記憶視窗差距過大的問題,也確認p型鐵電記憶體具有更為優異的可靠度表現。

此研究成果對於擴展鐵電記憶體的應用範圍並提高記憶體電路設計彈性/多樣性有相當大的助益,不僅刊登於IEEE Electron Device Letters期刊,更獲選為該期刊2021年6月的期刊封面(Journal Cover)與編輯精選(Editor’s Pick)。值得一提的是IEEE Electron Device Letters是微電子元件領域的頂尖期刊,在國際間享有權威的學術聲望與廣大的影響力,也是IEEE Electron Device Society所發行的旗艦期刊。該期刊以每個月一期的方式出刊,每年約刊登450篇來自於全世界頂尖研究團隊關於半導體元件的研究成果。每一期僅有一篇論文可獲選為期刊封面,在所有刊登的論文中獲選率低於3 %。

論文相關資訊:

Hao-Kai Peng, Tien-Hong Kao, Yu-Cheng Kao, Pin-Jiun Wu, and Yung-Hsien Wu, “Reduced Asymmetric Memory Window Between Si-Based n- and p-FeFETs With Scaled Ferroelectric HfZrOx and AlON Interfacial Layer,” IEEE Electron Device Letters, vol. 42, no. 6, pp. 835-838, 2021. DOI: 10.1109/LED.2021.3074434

編輯精選相關資訊:

https://www.facebook.com/IEEEElectronDevicesSociety/